Program

Schedule

Advanced Program

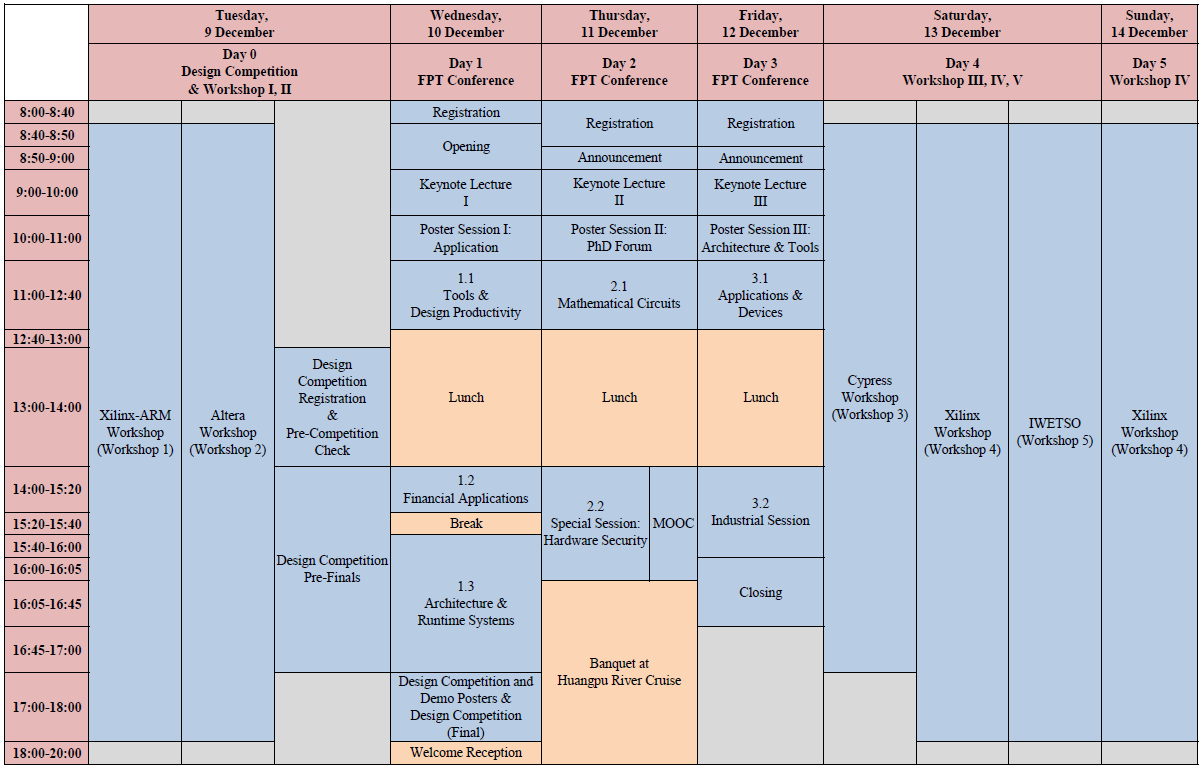

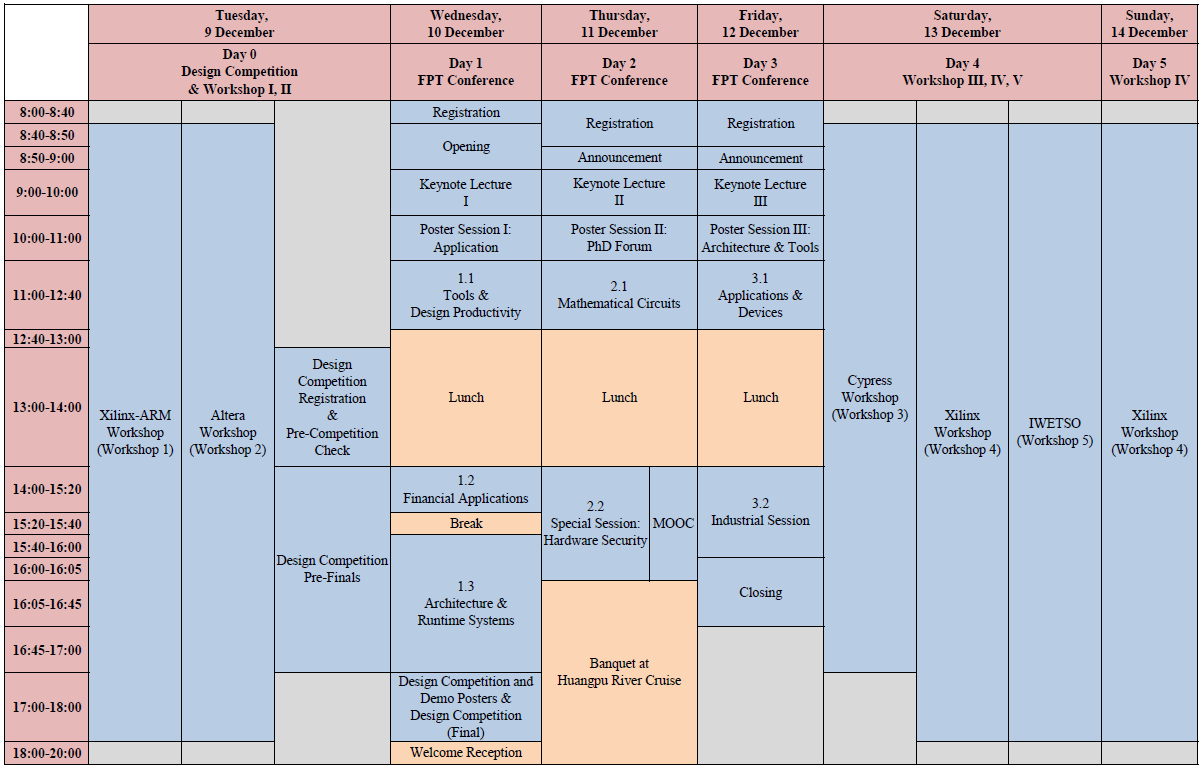

[Design Competition & Workshop I,II] Day 0 (Tuesday, 9 December)

| 13:00-14:00 |

| Design Competition Registration & Pre-Competition Check |

| Location: Parkyard Hotel |

|

| 14:00-17:00 |

| Design Competition Pre-Finals |

| Location: Ballroom, Parkyard Hotel |

|

[FPT Conference] Day 1 (Wednesday, 10 December)

| 8:00-8:40 |

Location: Parkyard Hotel |

|

Opening

Chairs: Lingli Wang, Fudan University

Hayden Kwok-Hay So, University of Hong Kong

|

| 8:40-9:00 |

Location: Ballroom, Parkyard Hotel |

| |

Location: Ballroom, Parkyard Hotel |

|

Poster Session I: Application

Session Chair: Tomonori Izumi, Ritsumeikan University

|

| 10:00-11:00 |

Location: Poster Area, Parkyard Hotel |

| |

| A Flexible Interface Architecture for Reconfigurable Coprocessors in Embedded Multicore Systems using PCIe Single-Root I/O Virtualization |

| Oliver Sander, Steffen Baehr, Enno Luebbers, Timo Sandmann, Viet Vu Duy and Juergen Becker |

|

| |

| Gigabyte-Scale Alignment Acceleration of Biological Sequences via Ethernet Streaming |

| Theepan Moorthy and Sathish Gopalakrishnan |

|

| |

| Power Modelling and Capping for Heterogeneous ARM/FPGA SoCs |

| Yun Wu, Jose Nunez-Yanez, Roger Woods and Dimitrios S. Nikolopoulos |

|

| |

| Analysis and Optimization of a Deeply Pipelined FPGA Soft Processor |

| Hui Yan Cheah, Suhaib A. Fahmy and Nachiket Kapre |

|

| |

| A Circuit to Synchronize High Speed Serial Communication Channel |

| Mrinal J Sarmah |

|

| |

| Novel Reconfigurable Hardware Implementation of Polynomial Matrix/Vector Multiplications |

| Server Kasap and Soydan Redif |

|

| |

| A Complementary Architecture for High-Speed True Random Number Generator |

| Xian Yang and Ray C.C. Cheung |

|

| |

| Fanout Decomposition Dataflow Optimizations for FPGA-based Sparse LU Factorization |

| Siddhartha and Nachiket Kapre |

|

| |

| Zero Latency Encryption with FPGAs for Secure Time-Triggered Automotive Networks |

| Shanker Shreejith and Suhaib A. Fahmy |

|

| |

| Using C to Implement High-efficient Computation of Dense Optical Flow on FPGA-accelerated Heterogeneous Platforms |

| Zhilei Chai, Haojie Zhou, Zhibin Wang and Dong Wu |

|

| |

| Hardware Architecture of Bi-Cubic Convolution Interpolation for Real-time Image Scaling |

| Gopinath Mahale, Hamsika Mahale, Rajesh Babu Parimi, S.K. Nandy and S. Bhattacharya |

|

| |

| FPGA-based High Throughput XTS-AES Encryption/Decryption for Storage Area Network |

| Yi Wang, Akash Kumar and Yajun Ha |

|

| |

| Zyndroid: An Android Platform for Software/Hardware Coprocessing |

| Susumu Mashimo, Motoki Amagasaki, Masahiro Iida, Morihiro Kuga and Toshinori Sueyoshi |

|

| |

| A Dataflow System for Anomaly Detection and Analysis |

| Andrei Bara, Xinyu Niu and Wayne Luk |

|

| |

| AMMC: Advanced Multi-core Memory Controller |

| Tassadaq Hussain, Oscar Palomar, Osman Unsal, Adrian Cristal, Eduard Ayguadé, Mateo Valero and S. A. Gursal |

|

|

1.1 Tools & Design Productivity

Session Chair: Brad Hutchings, Brigham Young University

|

| |

Location: Ballroom, Parkyard Hotel |

| 11:00-11:20 |

| Design Re-Use for Compile Time Reduction in FPGA High-Level Synthesis Flows(Best Paper Award) |

| Marcel Gort and Jason Anderson |

|

| 11:20-11:40 |

| Is High Level Synthesis Ready for Business? A Computational Finance Case Study |

| Gordon Inggs, Shane Fleming, David Thomas and Wayne Luk |

|

| 11:40-12:00 |

| Comparing Performance, Productivity and Scalability of the TILT Overlay Processor to OpenCL HLS |

| Rafat Rashid, J. Gregory Steffan and Vaughn Betz |

|

| 12:00-12:20 |

| Size Aware Placement for Island Style FPGAs |

| Junying Huang, Colin Yu Lin, Yang Liu, Zhihua Li and Haigang Yang |

|

| 12:20-12:40 |

| Analyzing the Impact of Heterogeneous Blocks on FPGA Placement Quality |

| Chang Xu, Wentai Zhang and Guojie Luo |

|

| 12:40-14:00 |

Location: Parkyard Hotel |

|

1.2 Financial Applications

Session Chair: Nachiket Kapre, Nanyang Technological University

|

| |

Location: Ballroom, Parkyard Hotel |

| 14:00-14:20 |

| Low-latency Option Pricing using Systolic Binomial Trees (Best Paper Candidate) |

| Aryan Tavakkoli and David B. Thomas |

|

| 14:20-14:40 |

| Collaborative Processing of Least-Square Monte Carlo for American Options |

| Jinzhe Yang, Ce Guo, Wayne Luk and Terence Nahar |

|

| 14:40-15:00 |

| Accelerating Transfer Entropy Computation |

| Shengjia Shao, Ce Guo, Wayne Luk and Stephen Weston |

|

| 15:00-15:20 |

| FPGA-accelerated Monte-Carlo Integration using Stratified Sampling and Brownian Bridges |

| Mark de Jong, Vlad-Mihai Sima, Koen Bertels and David Thomas |

|

| 15:20-15:40 |

Location: Parkyard Hotel |

|

1.3 Architecture & Runtime Systems

Session Chair: Paul Chow, University of Toronto

|

| |

Location: Ballroom, Parkyard Hotel |

| 15:40-16:00 |

| Time Sharing of Runtime Coarse-Grain Reconfigurable Architectures Processing Elements in Multi-Process Systems |

| Benjamin Carrion Schafer |

|

| 16:00-16:20 |

| Architectural Synthesis of Computational Pipelines with Decoupled Memory Access |

| Shaoyi Cheng and John Wawrzynek |

|

| 16:20-16:40 |

| Improve Memory Access for Achieving Both Performance and Energy Efficiencies on Heterogeneous Systems |

| Hongyuan Ding and Miaoqing Huang |

|

| 16:40-17:00 |

| Approaching Overhead-Free Execution on FPGA Soft-Processors |

| Charles Eric LaForest, Jason Anderson and J. Gregory Steffan |

|

| 17:00-18:00 |

Location: Poster Area, Parkyard Hotel |

| |

| Hardware/Software co-design Architecture for Blokus Duo Solver |

| Naru Sugimoto and Hideharu Amano |

|

| |

| Optimize MinMax Algorithm to solve Blokus Duo Game by HDL |

| Hossein Borhanifar and Seyed Peyman Zolnouri |

|

| |

| An Improved FPGA-based Specific Processor for Blokus Duo |

| Javier Olivito, Alberto Delmás and Javier Resano |

|

| |

| Highly Scalable, SharedMemory , Monte-Carlo Tree Search based Blokus Duo Solver on FPGA |

| Ehsan Qasemi, Amir Samadi, Mohammad H. Shadmehr, Bardia Azizian, Sajjad Mozaffari, Amir Shirian and Bijan Alizadeh |

|

| |

| Blokus Duo Engine on a Zynq |

| Susumu Mashimo, Kansuke Fukuda, Motoki Amagasaki, Masahiro Iida, Morihiro Kuga and Toshinori Sueyoshi |

|

| |

| FPGA Implementation of Blokus Duo Player using Hardware/Software Co-Design |

| Akira Kojima |

|

| |

| An FPGA Blokus Duo Solver with a High Activity |

| Takumi Fujimori, Retsu Moriwaki, Masato Seo, Kouta Akagi, Hiroyuki Ito, Takayuki Kubota, Shinya Furukawa, and Minoru Watanabe |

|

| |

| Stratics FPGA Blokus Duo Solver |

| Takumi Fujimori, Retsu Moriwaki, Masato Seo, Kouta Akagi, Hiroyuki Ito, Takayuki Kubota, Shinya Furukawa, and Minoru Watanabe |

|

| |

| An Improved FPGA Blokus Player via Alpha-Betha Pruning and Monte-Carlo Algorithm |

| Nariman Eskandari, Ali Jahanshahi and Mohammad Kazem Taram |

|

| |

| The Stochastic Blokus Duo Solver |

| Rie Soejima, Kota Aoki, Kaoru Hamasaki, Masahito Oishi, Koji Okina, Jimpei Hamamura, Shun Kashiwagi, Yoshiki Hayashida, Ryo Fujita, Yudai Shirakura, Fumihiko Iwasaki, Tai Noguchi, Aiko Iwasaki, Kota Fukumoto and Yuichiro Shibata |

|

| |

| Developing an FPGA Blokus Duo Solver By System-Level Design |

| Masataka Ogawa, Yuki Ando, Shinya Honda, Go Sato and Yusuke Kato |

|

| |

| Blokus Duo Player Based on ZYBO |

| Song Xu and Lin Wang |

|

| |

| BLUE STORM-Blokus Unified Engine of Search and Test Operation by RitsuMei |

| Masashi Ohno, Yuu Nakahara, Kazuya Ohtsu, Tatsuya Suzuki, Tomonori Izumi and Meng Lin |

|

| |

| An Implementation of Multi Game AI System of Blokus Duo on FPGA with NSL |

| Ryo Tamaki |

|

|

Demo Session

Session Chair: Hao Zhou, Fudan University

|

| 17:00-18:00 |

Location: Poster Area, Parkyard Hotel |

| |

| Network Recorder and Player:FPGA-based Network Traffic Capture and Replay |

| Siyi Qiao, Chen Xu, Lei Xie, Ji Yang, Chengchen Hu, Xiaohong Guan and Jianhua Zhou |

|

| |

| Implementation of LS-SVM with HLS on Zynq |

| Ma Ning, Wang Shaojun, Pang Yeyong and Peng Yu |

|

| |

| A High-performance and High-programmability Reconfigurable Wireless Development Platform |

| Jiahua Chen, Tao Wang, Haoyang Wu, Jian Gong, Xiaoguang Li, Yang Hu, Gaohan Zhang, Zhiwei Li, Junrui Yang and Songwu Lu |

|

| |

| Image Processing by a 0.3V 2MW Coarse-Grained Reconfigurable Accelerator CMA-SOTB with a Solar Battery |

| Yu Fujita, Koichiro Masuyama and Hideharu Amano |

|

| 17:00-18:00 |

Location: Ballroom A, Parkyard Hotel |

| 18:00-20:00 |

Location: Phoenix |

[FPT Conference] Day 2 (Thursday, 11 December)

| 8:00-8:50 |

Location: Parkyard Hotel |

| 8:50-9:00 |

Location: Ballroom, Parkyard Hotel |

| |

Location: Ballroom, Parkyard Hotel |

|

Poster Session II: PhD Forum

Session Chair: Yu Hu, Chinese Academy of Sciences

|

| 10:00-11:00 |

Location: Poster Area, Parkyard Hotel |

| |

| Design Space Exploration for FPGA-based Hybrid Multicore Architecture |

| Jian Yan, Junqi Yuan, Ying Wang, Philip Leong and Lingli Wang |

|

| |

| Reducing the Overhead of Dynamic Partial Reconfiguration for Multi-mode Circuits |

| Brahim Al Farisi, Karel Heyse and Dirk Stroobandt |

|

| |

| HW Acceleration of Multiple Applications on a Single FPGA |

| Yidi Liu and Benjamin Carrion Schafer |

|

| |

| Towards Automatic Partial Reconfiguration in FPGAs |

| Fubing Mao, Wei Zhang and Bingsheng He |

|

| |

| Achieving Higher Performance of Memcached by Caching at Network Interface |

| Eric S. Fukuda, Hiroaki Inoue, Takashi Takenaka, Dahoo Kim, Tsunaki Sadahisa, Tetsuya Asai and Masato Motomura |

|

| |

| No Zero Padded Sparse Matrix-Vector Multiplication on FPGAs |

| Jiasen Huang, Junyan Ren, Wenbo Yin and Lingli Wang |

|

|

2.1 Mathematical Circuits

Session Chair: Donald Bailey, Massey University

|

| |

Location: Ballroom, Parkyard Hotel |

| 11:00-11:20 |

| Low-Latency Double-Precision Floating-Point Division for FPGAs |

| Björn Liebig and Andreas Koch |

|

| 11:20-11:40 |

| Efficient FPGA Implementation of Digit Parallel Online Arithmetic Operators (Best Paper Candidate) |

| Kan Shi, David Boland and George A. Constantinides |

|

| 11:40-12:00 |

| An Efficient FPGA Implementation of QR Decomposition using a Novel Systolic Array Architecture based on Enhanced Vectoring CORDIC |

| Jianfeng Zhang, Paul Chow and Hengzhu Liu |

|

| 12:00-12:20 |

| Area Efficient Floating Point Adder and Multiplier with IEEE-754 Compatible Semantics |

| Andreas Ehliar |

|

| 12:20-12:40 |

| A Universal FPGA-based Floating-point Matrix Processor for Mobile Systems |

| Wenqiang Wang, Kaiyuan Guo, Mengyuan Gu, Yuchun Ma and Yu Wang |

|

| 12:40-14:00 |

Location: Parkyard Hotel |

|

2.2 Special Session: Hardware Security

Session Chair: Yongqiang Lyu, Tsinghua University

|

| |

Location: Ballroom, Parkyard Hotel |

| 14:00-14:25 |

| A Survey on Security and Trust of FPGA-based Systems |

| Jiliang Zhang and Gang Qu |

|

| 14:25-14:50 |

| Hardware Trojan Detection Acceleration Based on Word-Level Statistical Properties Management |

| He Li and Qiang Liu |

|

| 14:50-15:15 |

| Power Supply Noise Aware Evaluation Framework for Side Channel Attacks and Countermeasures |

| Jianlei Yang, Chenguang Wang, Yici Cai and Qiang Zhou |

|

| 15:15-15:40 |

| Memory Security in Reconfigurable Computers: Combining Formal Verification with Monitoring |

| Tobias Wiersema, Stephanie Drzevitzky and Marco Platzner |

|

| 15:40-16:05 |

| An FPGA-based Spectral Anomaly Detection System |

| Duncan J.M. Moss, Zhe Zhang, Nicholas J Fraser and Philip H.W. Leong |

|

|

MOOC

Session Chair: Manfred Glesner, Technische Universitat Darmstadt

|

| 14:00-16:05 |

Location: Meeting Room 1, Parkyard Hotel |

| Banquet at Huangpu River Cruise |

| 16:05-20:00 |

Location: East Fuxing Road, the ferry (307 Waima Road, near Baidu Road)

地点:复兴东路轮渡口(外马路307号近白渡路)

|

[FPT Conference] Day 3 (Friday, 12 December)

| 8:00-8:50 |

Location: Parkyard Hotel |

| 8:50-9:00 |

Location: Ballroom, Parkyard Hotel |

| |

Location: Ballroom, Parkyard Hotel |

|

Poster Session III: Architecture & Tools

Session Chair: Kentaro Sato, Tohoku University

|

| 10:00-11:00 |

Location: Poster Area, Parkyard Hotel |

| |

| Assessing Scrubbing Techniques for Xilinx SRAM-based FPGAs in Space Applications |

| Fredrik Brosser, Emil Milh, Vilhelm Geijer and Per Larsson-Edefors |

|

| |

| A Fast, Energy Efficient, Field Programmable Threshold-Logic Array |

| Niranjan Kulkarni, Jinghua Yang and Sarma Vrudhula |

|

| |

| A Novel Three-dimensional FPGA Architecture with High-speed Serial Communication Links |

| Takuya Kajiwara, Qian Zhao, Motoki Amagasak, Masahiro Iida, Morihiro Kuga and Toshinori Sueyoshi |

|

| |

| Scalable Radio Processor Architecture for Modern Wireless Communications |

| Young-Hwan Park, Keshava Prasad, Yeonbok Lee, Kitaek Bae and Ho Yang |

|

| |

| Integrating FPGA-based Processing Elements into a Runtime for Parallel Heterogeneous Computing |

| David de la Chevallerie, Jens Korinth and Andreas Koch |

|

| |

| Deep and Narrow Binary Content-Addressable Memories using FPGA-based BRAMs |

| Ameer M.S. Abdelhadi and Guy G.F. Lemieux |

|

| |

| Development Productivity in Implementing a Complex Heterogeneous Computing Application |

| Anthony Milton, David Kearney, Sebastien Wong and Simon Lemmo |

|

| |

| Real-time 3D Reconstruction for FPGAs: A Case Study for Evaluating the Performance, Area, and Programmability Trade-offs of the Altera OpenCL SDK |

| Quentin Gautier, Alexandria Shearer, Janarbek Matai, Dustin Richmond, Pingfan Meng and Ryan Kastner |

|

| |

| Online Scheduling for FPGA Computation in the Cloud |

| Guohao Dai, Yi Shan, Fei Chen, Yu Wang, Kun Wang and Huazhong Yang |

|

| |

| High Performance Relevance Vector Machine on HMPSoC |

| Yongfu He, Shaojun Wang, Yu Peng, Yeyong Pang, Ning Ma and Jingyue Pang |

|

| |

| Improving the Reliability of RO PUF using Frequency Offset |

| Bin Tang, Yaping Lin and Jiliang Zhang |

|

|

3.1 Applications & Devices

Session Chair: Andre DeHon, University of Pennsylvania

|

| |

Location: Ballroom, Parkyard Hotel |

| 11:00-11:20 |

| ROTORouter: Router Support for Endpoint-Authorized Decentralized Traffic Filtering to Prevent DoS Attacks |

| Albert Kwon, Kaiyu Zhang, Perk Lun Lim, Yuchen Pan, Jonathan M. Smith and André DeHon |

|

| 11:20-11:40 |

| Parallel Resampling for Particle Filters on FPGAs |

| Shuanglong Liu, Grigorios Mingas and Christos-Savvas Bouganis |

|

| 11:40-12:00 |

| Evaluation of SNMP-like protocol to manage a NoC Emulation Platform |

| Otávio Alcântara de Lima Junior, Virginie Fresse and Frédéric Rousseau |

|

| 12:00-12:20 |

| A High-Performance Low-Power Near-Vt RRAM-based FPGA (Best Paper Candidate) |

| Xifan Tang, Pierre-Emmanuel Gaillardon and Giovanni De Micheli |

|

| 12:20-12:40 |

| A Pure-CMOS Nonvolatile Multi-Context Configuration Memory for Dynamically Reconfigurable FPGAs |

| Kosuke Tatsumura, Masato Oda and Shinichi Yasuda |

|

| 12:40-14:00 |

Location: Parkyard Hotel |

| |

Location: Ballroom, Parkyard Hotel |

| 14:00-14:20 |

| Programmable Multimedia Platform based on Samsung Reconfigurable Processor |

| Sukjin Kim, Samsung |

|

| 14:20-14:40 |

| Staying a Generation Ahead |

| Jason Wong, Xilinx |

|

| 16:00-16:45 |

Location: Ballroom, Parkyard Hotel |

[Workshop III, IV, V] Day 4 (Saturday, 13 December)

| All day |

| Workshop 4: Xilinx Workshop "OpenCV Application Acceleration with Vivado High Level Synthesis" |

| Location: Room 101, Computer Building, Zhangjiang Campus, Fudan University |

|

[Workshop IV] Day 5 (Sunday, 14 December)

| 8:30-12:00 |

| Workshop 4: Xilinx Workshop "OpenCV Application Acceleration with Vivado High Level Synthesis" |

| Location: Room 101, Computer Building, Zhangjiang Campus, Fudan University |

|